### SCALABLE SUPPORT FOR PROCESS-ORIENTED PROGRAMMING

A THESIS SUBMITTED TO THE UNIVERSITY OF KENT IN THE SUBJECT OF COMPUTER SCIENCE FOR THE DEGREE OF DOCTOR OF PHILOSOPHY.

> By Carl G. Ritson 2013

### Abstract

Process-oriented programming is a method for applying a high degree of concurrency within software design while avoiding associated pitfalls such as deadlocks and race hazards. A process-oriented computer program contains multiple distinct software processes which execute concurrently. All interaction between processes, including information exchange, occurs via explicit communication and synchronisation mechanisms. The explicit nature of interaction in process-oriented programming underpins its ability to provide manageable concurrency. These interaction mechanisms represent both a potential overhead in the execution of process-oriented software and a point of mechanical sympathy with emerging multi-core computer architectures. This thesis details engineering to reduce the overheads associated with a process-oriented style of software design and evaluate its mechanical sympathy.

The first half of this thesis provides an in-depth review of facilities for concurrent programming and their support in programming languages. Common concurrent programming facilities are defined and their relationship to process-oriented design established. It contains an analysis of the significance of mechanical sympathy in programming languages, trends in hardware and software design, and relates these to process-oriented programming.

The latter part of this thesis describes techniques for the compilation and execution of process-oriented software on multi-core hardware so as to achieve the maximum utilisation of parallel computing resources with the minimum overhead from process-oriented interaction mechanisms. A new runtime kernel design for the occampi programming language is presented and evaluated. This design enables efficient cache-affine work-stealing scheduling of processes on multi-core hardware using waitfree and non-blocking algorithms. This is complemented by modern compilation techniques for occam-pi program code using machine independent assembly to improve performance and portability, and methods for debugging the execution of processoriented software using a virtual machine interpreter. Through application, these methods prove the mechanical sympathy and parallel execution potential of a process-oriented software.

### Acknowledgements

I began this PhD while working as a research associate on the RMoX project under the direction of Fred Barnes. My work owes much to Fred Barnes as both my supervisor and the author of much of the prior work and computer code on which this thesis builds.

My research has been supported financially by the EPSRC funded projects RMoX (EP/D061822/1) and CoSMoS (EP/E049419/1). I have also received financial support from the University of Kent's staff development fund and the School of Computing.

The community of researchers interested in concurrency at Kent was a significant motivation to me and I am sad to see that that the Concurrency Research Group has all but ceased to exist. Peter Welch and his enthusiasm has been the hub for much concurrency research at Kent. He inspired and encouraged me to pursue research in this area. Christian Jacobsen, Matt Jadud and Damian Dimmich's work on the Transterpreter provided an excellent test bed for many of my ideas and good source of code for me to rewrite. Adam Sampson's input and feedback on my work has proved invaluable. Jon Simpson with whom I have shared an office and the path of PhD student has always been a good source of moral support and pragmatism.

Utmost I would like my family, close friends and especially Jasmine. All of whom have always been there offering their support.

## Contents

| Ał | ii ii   |                   |

|----|---------|-------------------|

| Ac | knov    | vledgements iv    |

| Co | onten   | ts v              |

| Li | st of . | Algorithms xvii   |

| Li | st of ] | Figures xviii     |

| Li | st of ' | Tables xxi        |

| 1  | Intr    | oduction 1        |

|    | 1.1     | Problem Statement |

|    | 1.2     | Limitations       |

|    | 1.3     | Contributions     |

|    | 1.4     | Road Map 5        |

| 2  | Con     | currency 7        |

|    | 2.1     | Motivations       |

|    |         | 2.1.1 Expression  |

|     | 2.1.2  | Perform  | nance                                  | 16 |

|-----|--------|----------|----------------------------------------|----|

|     | 2.1.3  | Timelin  | ess                                    | 17 |

|     |        | 2.1.3.1  | Energy Usage                           | 18 |

|     |        | 2.1.3.2  | Parallelism                            | 19 |

|     |        | 2.1.3.3  | Processor Development Trends           | 20 |

| 2.2 | Parad  | igms     |                                        | 24 |

|     | 2.2.1  | Data-or  | iented                                 | 25 |

|     |        | 2.2.1.1  | Vectorization                          | 27 |

|     |        | 2.2.1.2  | Transactional Memory                   | 28 |

|     |        | 2.2.1.3  | Partitioned Global Address Space       | 30 |

|     | 2.2.2  | Message  | e-passing                              | 31 |

|     | 2.2.3  | Other P  | aradigms                               | 33 |

| 2.3 | Primit | tives    |                                        | 35 |

|     | 2.3.1  | Processe | es                                     | 35 |

|     |        | 2.3.1.1  | Threads and Fibers                     | 36 |

|     |        | 2.3.1.2  | Actors, Objects and Agents             | 37 |

|     |        | 2.3.1.3  | Closures, Coroutines and Continuations | 38 |

|     |        | 2.3.1.4  | Scheduling and Priority                | 40 |

|     |        | 2.3.1.5  | Performance                            | 44 |

|     | 2.3.2  | Commu    | inication and Synchronisation          | 46 |

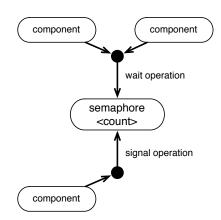

|     |        | 2.3.2.1  | Semaphores and Monitors                | 46 |

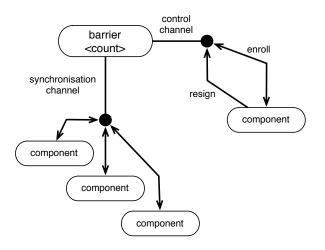

|     |        | 2.3.2.2  | Barriers                               | 51 |

|     |        | 2.3.2.3  | Interrupts, Signals and Events         | 54 |

|     |        | 2.3.2.4  | Messages, Mailboxes and Channels       | 58 |

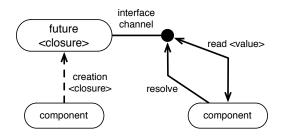

|     |        | 2.3.2.5  | Promises and Futures                   | 65 |

|     | 2.3.3  | Choice   |                                        | 67 |

|     |        | 2.3.3.1  | Determinism                            | 68 |

|     |        | 2.3.3.2  | Programming Language Support           | 70 |

|     |        | 2.3.3.3  | Commitment                             | 72 |

|     |        | 2.3.3.4    | Time                            |   | '4         |

|-----|--------|------------|---------------------------------|---|------------|

|     |        | 2.3.3.5    | Summary                         |   | <b>'</b> 4 |

| 2.4 | Proces | s-oriente  | d Programming                   | 7 | <b>'</b> 4 |

|     | 2.4.1  | Primitiv   | res                             | 7 | 6          |

|     |        | 2.4.1.1    | Asynchronous Channels           | 7 | 7          |

|     |        | 2.4.1.2    | Shared Memory                   | 7 | 7          |

|     |        | 2.4.1.3    | Semaphores                      | 7 | 78         |

|     |        | 2.4.1.4    | Monitors                        | 7 | '8         |

|     |        | 2.4.1.5    | Actor Model                     | 7 | '9         |

|     |        | 2.4.1.6    | Futures                         | 7 | '9         |

|     |        | 2.4.1.7    | Barriers                        | 8 | 80         |

| 2.5 | Concu  | irrency Su | upport in Programming Languages | 8 | 1          |

|     | 2.5.1  | Keyword    | ds                              | 8 | 32         |

|     | 2.5.2  | Ada        |                                 | 8 | 33         |

|     | 2.5.3  | Alice .    |                                 | 8 | 34         |

|     | 2.5.4  | С          |                                 | 8 | 84         |

|     | 2.5.5  | C#         |                                 | 8 | 85         |

|     | 2.5.6  | C++        |                                 | 8 | 35         |

|     | 2.5.7  | Chapel     |                                 | 8 | 6          |

|     | 2.5.8  | Cilk       |                                 | 8 | 87         |

|     | 2.5.9  | Clojure    |                                 | 8 | 88         |

|     | 2.5.10 | Concurr    | rent ML                         | 8 | 88         |

|     | 2.5.11 | Erlang     |                                 | 8 | 9          |

|     | 2.5.12 | Fortress   |                                 | 8 | 9          |

|     | 2.5.13 | Google (   | Go                              | 9 | 0          |

|     | 2.5.14 | GPGPU:     | CUDA and OpenCL                 | 9 | 1          |

|     | 2.5.15 | Haskell    |                                 | 9 | 2          |

|     | 2.5.16 | Intel Th   | read Building Blocks            | 9 | 2          |

|     | 2.5.17 | Java       |                                 | 9 | 93         |

|     | 2.5.18  | Manticore                                  | 94  |

|-----|---------|--------------------------------------------|-----|

|     | 2.5.19  | Message Passing Interface                  | 95  |

|     | 2.5.20  | Objective-C                                | 95  |

|     | 2.5.21  | occam                                      | 96  |

|     | 2.5.22  | OpenMP                                     | 97  |

|     | 2.5.23  | Parallel Virtual Machine                   | 98  |

|     | 2.5.24  | POSIX Threads                              | 99  |

|     | 2.5.25  | Rust                                       | 99  |

|     | 2.5.26  | Scala                                      | 100 |

|     |         | 2.5.26.1 Akka                              | 101 |

|     | 2.5.27  | Smalltalk                                  | 101 |

|     | 2.5.28  | Unified Parallel C                         | 102 |

|     | 2.5.29  | X10                                        | 102 |

|     | 2.5.30  | XMOS XC                                    | 103 |

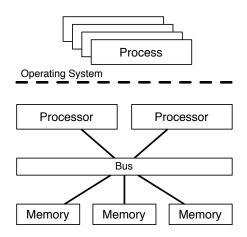

| 2.6 | Concu   | rrency Support in Hardware                 | 104 |

|     | 2.6.1   | Synchronisation                            | 110 |

|     |         | 2.6.1.1 Measurement Methodology            | 113 |

|     | 2.6.2   | Interconnects                              | 113 |

| 2.7 | Analy   | sis                                        | 115 |

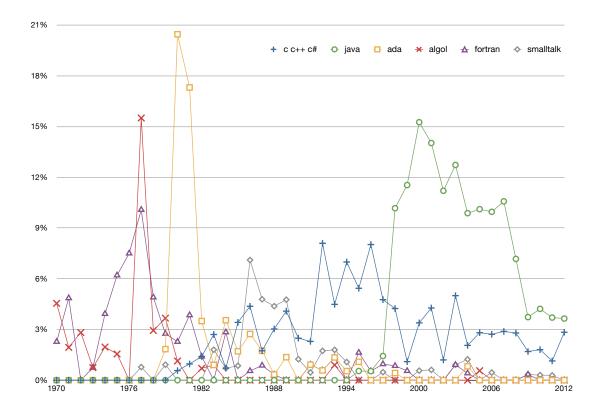

|     | 2.7.1   | Popularity                                 | 115 |

|     | 2.7.2   | The Popularity of C                        | 117 |

|     | 2.7.3   | Trends in Academia                         | 121 |

|     | 2.7.4   | Industrial Influence                       | 124 |

|     | 2.7.5   | Summary                                    | 125 |

| Sch | eduling |                                            | 128 |

| 3.1 | occam   | ·<br>· · · · · · · · · · · · · · · · · · · | 128 |

| 3.2 | occam   | -pi                                        | 130 |

| 3.3 |         | -<br>Work                                  | 131 |

| 3.4  | Desigr | n Goals                     | 134 |

|------|--------|-----------------------------|-----|

|      | 3.4.1  | Work Stealing               | 134 |

|      | 3.4.2  | Working Set Batches         | 137 |

| 3.5  | KRoC   |                             | 138 |

| 3.6  | Algori | thms and Conventions        | 141 |

| 3.7  | Proces | ses                         | 143 |

|      | 3.7.1  | Scheduling                  | 145 |

|      | 3.7.2  | Batches                     | 147 |

|      | 3.7.3  | Batch Size                  | 149 |

| 3.8  | Run-q  | ueues and Process Migration | 150 |

|      | 3.8.1  | Local Enqueue               | 153 |

|      | 3.8.2  | Local Dequeue               | 154 |

|      | 3.8.3  | Remote Dequeue              | 155 |

|      | 3.8.4  | Laundry                     | 155 |

|      | 3.8.5  | Work Stealing               | 156 |

|      | 3.8.6  | Priority                    | 157 |

|      | 3.8.7  | Affinity                    | 157 |

|      | 3.8.8  | Blocking System Calls       | 158 |

|      | 3.8.9  | Mailboxes                   | 159 |

| 3.9  | Comm   | nunication                  | 161 |

| 3.10 | Timers | 5                           | 162 |

|      | 3.10.1 | Timer Expiration            | 164 |

| 3.11 | Altern | ation                       | 164 |

|      | 3.11.1 | Initialisation              | 169 |

|      | 3.11.2 | Channel Enabling            | 170 |

|      | 3.11.3 | Timer Enabling              | 170 |

|      | 3.11.4 | Waiting for Events          | 171 |

|      | 3.11.5 | Channel Disabling           | 171 |

|      | 3.11.6 | Timer Disabling             | 172 |

|      |        |                             |     |

|   |      | 3.11.7  | Finalisation              | 173        |

|---|------|---------|---------------------------|------------|

|   |      | 3.11.8  | Event Trigger Algorithm   | 173        |

|   | 3.12 | Extenc  | ded Rendezvous            | 173        |

|   | 3.13 | Mutua   | al Exclusion              | 175        |

|   |      | 3.13.1  | Operation and Correctness | 179        |

|   | 3.14 | Barrier | rs                        | 181        |

|   |      | 3.14.1  | Enrollment                | 182        |

|   |      | 3.14.2  | Resignation               | 182        |

|   |      | 3.14.3  | Synchronisation           | 184        |

|   |      | 3.14.4  | Completion                | 184        |

|   |      | 3.14.5  | Correctness               | 188        |

|   | 3.15 | Evalua  | ation                     | 189        |

|   |      | 3.15.1  | Test Setup                | 189        |

|   |      | 3.15.2  | Mandelbrot                | 190        |

|   |      | 3.15.3  | Process Ring              | 191        |

|   |      | 3.15.4  | Agent Simulation          | 193        |

|   |      | 3.15.5  | Performance Counters      | 197        |

|   | 3.16 | Conclu  | usions                    | 212        |

| 4 | Com  | pilatio | m                         | 213        |

| - | 4.1  | -       | ation                     | 213        |

|   | 4.2  |         |                           | 215        |

|   |      |         | D LLVM Translation        | 217        |

|   | 1.0  | 4.3.1   | Stack to SSA              | 217        |

|   |      | 4.3.2   | Process Representation    | 219        |

|   |      | 4.3.3   | Calling Conventions       | 223        |

|   |      | 4.3.4   | Branching and Labels      | 223<br>224 |

|   |      | 4.3.5   | Symbol Naming             | 224        |

|   |      | 4.3.6   |                           | 227        |

|   |      | 1.0.0   |                           | <u> </u>   |

|   |      | 4.3.7   | Floating Point                | 227 |

|---|------|---------|-------------------------------|-----|

|   | 4.4  | Analy   | <i>r</i> sis                  | 228 |

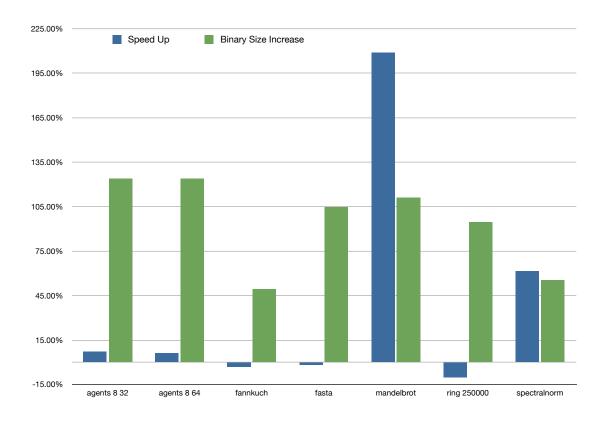

|   |      | 4.4.1   | agents                        | 229 |

|   |      | 4.4.2   | fannkuch                      | 230 |

|   |      | 4.4.3   | fasta                         | 230 |

|   |      | 4.4.4   | mandelbrot                    | 231 |

|   |      | 4.4.5   | ring                          | 231 |

|   |      | 4.4.6   | spectralnorm                  | 231 |

|   |      | 4.4.7   | Code Size                     | 232 |

|   |      | 4.4.8   | Summary                       | 232 |

|   | 4.5  | Concl   | usions                        | 233 |

|   |      |         |                               |     |

| 5 | Intr | ospecti | on                            | 235 |

|   | 5.1  | Motiv   | ration                        | 235 |

|   | 5.2  | Relate  | ed Work                       | 237 |

|   | 5.3  | The Tr  | ransterpreter Virtual Machine | 239 |

|   | 5.4  | Intros  | pection                       | 240 |

|   |      | 5.4.1   | Interface                     | 241 |

|   |      |         | 5.4.1.1 run                   | 243 |

|   |      |         | 5.4.1.2 step                  | 243 |

|   |      |         | 5.4.1.3 dispatch              | 244 |

|   |      |         | 5.4.1.4 get.state / set.state | 244 |

|   |      |         | 5.4.1.5 read / write          | 244 |

|   | 5.5  | Byteco  | ode                           | 244 |

|   |      | 5.5.1   | Encoding                      | 245 |

|   |      | 5.5.2   | Structure                     | 246 |

|   |      | 5.5.3   | In-place Decoding             | 248 |

|   |      | 5.5.4   | Interface                     | 248 |

|   |      |         | 5.5.4.1 create.vm             | 249 |

|   |            |                                                          | 5.5.4.2                                                               | get                  | c.file                        |         |                                                                        | •••   | •••            | •••     |         | • •            | • •            | • •                   | • •                   | •     | •          |                | • | 249                                           |

|---|------------|----------------------------------------------------------|-----------------------------------------------------------------------|----------------------|-------------------------------|---------|------------------------------------------------------------------------|-------|----------------|---------|---------|----------------|----------------|-----------------------|-----------------------|-------|------------|----------------|---|-----------------------------------------------|

|   |            |                                                          | 5.5.4.3                                                               | get                  | t.line                        | .info   |                                                                        |       |                | •••     |         |                |                |                       |                       | •     | •          |                | • | 249                                           |

|   |            |                                                          | 5.5.4.4                                                               | get                  | t.sym                         | ıbol ,  | / get                                                                  | sym   | bol            | at      |         |                |                |                       |                       | •     | •          |                |   | 249                                           |

|   |            |                                                          | 5.5.4.5                                                               | get                  | t.tlp                         |         |                                                                        |       |                | •••     |         |                |                |                       |                       | •     | •          |                |   | 251                                           |

|   | 5.6        | Debug                                                    | ging Sup                                                              | ppor                 | t                             |         |                                                                        | • •   |                |         |         |                |                |                       |                       | •     | •          |                |   | 251                                           |

|   |            | 5.6.1                                                    | The Pro                                                               | be E                 | ffect                         |         |                                                                        |       |                | •••     |         |                |                |                       |                       | •     | •          |                | • | 251                                           |

|   |            | 5.6.2                                                    | Memory                                                                | y Sha                | adow                          | ving    |                                                                        |       |                | •••     |         |                |                |                       |                       | •     | . <b>.</b> |                | • | 252                                           |

|   | 5.7        | A Trac                                                   | ing Debu                                                              | ugge                 | r.                            |         |                                                                        |       |                |         |         |                |                |                       |                       | •     | · •        |                | • | 254                                           |

|   |            | 5.7.1                                                    | Instanci                                                              | ing E                | 3ytec                         | ode     |                                                                        |       |                |         |         |                |                |                       |                       | •     | · •        |                | • | 254                                           |

|   |            | 5.7.2                                                    | Executir                                                              | ng B                 | ytecc                         | ode .   |                                                                        |       |                | • •     |         |                |                |                       |                       | •     | •          |                |   | 254                                           |

|   |            | 5.7.3                                                    | Tracking                                                              | g Pro                | ocess                         | es .    |                                                                        |       |                |         |         |                |                |                       |                       | •     | , <b>.</b> |                |   | 255                                           |

|   |            | 5.7.4                                                    | Visualis                                                              | satio                | n                             |         |                                                                        |       |                |         |         |                |                |                       |                       | •     | , <b>.</b> |                |   | 256                                           |

|   | 5.8        | Conclu                                                   | usions .                                                              |                      |                               |         |                                                                        |       |                |         |         |                |                |                       |                       | •     | , <b>.</b> |                |   | 259                                           |

|   |            |                                                          |                                                                       |                      |                               |         |                                                                        |       |                |         |         |                |                |                       |                       |       |            |                |   |                                               |

| 6 | Con        | clusion                                                  | s and Fu                                                              | ırthe                | r Wo                          | rk      |                                                                        |       |                |         |         |                |                |                       |                       |       |            |                |   | 261                                           |

|   | 6.1        | Overv                                                    | iew                                                                   | •••                  |                               |         |                                                                        |       |                | •••     |         |                |                |                       |                       | •     | •          |                | • | 261                                           |

|   | 6.2        | Specifi                                                  | ic Improv                                                             | veme                 | ents                          |         |                                                                        | • •   |                | •••     |         |                |                |                       |                       | •     | •          |                |   | 262                                           |

|   | 6.3        | Hetero                                                   | ogeneous                                                              | 3 Arc                | hitec                         | tures   | 5                                                                      |       |                | •••     |         |                |                |                       |                       | •     | · •        |                | • | 264                                           |

|   | 6.4        | Runtin                                                   | ne Embe                                                               | ddir                 |                               |         |                                                                        |       |                |         |         |                |                |                       |                       |       |            |                |   | 266                                           |

|   | 6.5        |                                                          |                                                                       |                      | ıg.                           |         |                                                                        | •••   | •••            | •••     |         |                | • •            |                       |                       | •     | •          |                | • | 200                                           |

|   |            | New L                                                    | anguage                                                               |                      | -                             |         |                                                                        |       |                |         |         |                |                |                       |                       |       |            |                |   | 267                                           |

|   | 6.6        |                                                          |                                                                       | es.                  |                               |         |                                                                        |       |                | •••     |         |                |                |                       |                       | •     |            |                |   |                                               |

|   | 6.6        |                                                          | anguage                                                               | es.                  |                               |         |                                                                        |       |                | •••     |         |                |                |                       |                       | •     |            |                |   | 267                                           |

| A |            |                                                          | .anguage<br>g Remarl                                                  | es.                  |                               |         |                                                                        |       |                | •••     |         |                |                |                       |                       | •     |            |                | • | 267                                           |

| A | Run        | Closin<br>time In                                        | .anguage<br>g Remarl                                                  | es .<br>·ks          |                               |         |                                                                        |       |                | •••     |         |                |                |                       |                       | • ·   |            |                | • | 267<br>269                                    |

| A | Run        | Closin<br><b>time In</b><br>Callinş                      | Language<br>g Remarl<br>A <b>terface</b>                              | es .<br>·ks<br>ntior |                               | · · · · |                                                                        | · · · | · · ·          | • • •   |         |                |                | · · ·                 | · · ·                 | • ·   |            | · · ·          | • | 267<br>269<br><b>270</b>                      |

| Α | Run        | Closin<br><b>time In</b><br>Callinş<br>A.1.1             | Language<br>g Remarl<br>I <b>terface</b><br>g Conver                  | es .<br>ks<br>ntior  | · · · ·<br>· · · ·            | · · · · | · · · ·                                                                | · · · | · · ·          | • • •   | · · · · | · · ·          | · · ·          | · · ·                 | · · ·                 | • •   | · ·        | · · ·          | • | 267<br>269<br><b>270</b><br>270               |

| Α | Run<br>A.1 | Closin<br>time In<br>Callinş<br>A.1.1<br>A.1.2           | Language<br>g Remarl<br>I <b>terface</b><br>g Conver<br>tranx86       | es .<br>ks<br>ntior  | · · · ·<br>· · · ·            | · · · · | · · · ·                                                                | · · · | · · ·          | • • •   | · · · · | · · ·<br>· ·   | · · ·<br>· · · | · · ·                 | · · ·                 | • •   | · · ·      | · · ·          | • | 267<br>269<br><b>270</b><br>270<br>270        |

| A | Run<br>A.1 | Closin<br>time In<br>Callins<br>A.1.1<br>A.1.2<br>Proces | anguage<br>g Remarl<br>t <b>erface</b><br>g Conver<br>tranx86<br>LLVM | es .<br>ks<br>ntior  | · · · ·<br>· · · ·<br>· · · · | · · · · | <ul> <li></li> <li></li> <li></li> <li></li> <li></li> <li></li> </ul> | · · · | · · ·<br>· · · | · · · · | · · · · | · · ·<br>· · · | · · ·<br>· · · | · · ·<br>· · ·<br>· · | · · ·<br>· · ·<br>· · | • · · | · · ·      | · · ·<br>· · · | • | 267<br>269<br><b>270</b><br>270<br>270<br>271 |

|     | A.2.3  | pause         | 272 |

|-----|--------|---------------|-----|

|     | A.2.4  | par_enroll    | 273 |

|     | A.2.5  | proc_alloc    | 273 |

|     | A.2.6  | proc_mt_copy  | 273 |

|     | A.2.7  | proc_mt_move  | 274 |

|     | A.2.8  | proc_param    | 274 |

|     | A.2.9  | proc_start    | 274 |

|     | A.2.10 | runp          | 275 |

|     | A.2.11 | startp        | 275 |

|     | A.2.12 | stopp         | 275 |

| A.3 | Mobile | es            | 276 |

|     | A.3.1  | malloc        | 276 |

|     | A.3.2  | mrelease      | 276 |

|     | A.3.3  | mt_alloc      | 276 |

|     | A.3.4  | mt_bind       | 277 |

|     | A.3.5  | mt_clone      | 277 |

|     | A.3.6  | mt_dclone     | 277 |

|     | A.3.7  | $mt_{enroll}$ | 278 |

|     | A.3.8  | $mt\_lock$    | 278 |

|     | A.3.9  | mt_release    | 278 |

|     | A.3.10 | mt_resign     | 278 |

|     | A.3.11 | mt_resize     | 279 |

|     | A.3.12 | mt_sync       | 279 |

|     | A.3.13 | $mt_{unlock}$ | 279 |

| A.4 | Chann  | nels          | 280 |

|     | A.4.1  | xable         | 280 |

|     | A.4.2  | xend          | 280 |

|     | A.4.3  | in            | 280 |

|     | A.4.4  | in32          | 280 |

|     | A.4.5 i  | in8 .  |           | • • | ••• |     | <br> | <br> | <br>• | <br> | • | ••• |  | • | • |     | 281 |

|-----|----------|--------|-----------|-----|-----|-----|------|------|-------|------|---|-----|--|---|---|-----|-----|

|     | A.4.6 x  | xin .  |           | ••  | ••  |     | <br> | <br> | <br>• | <br> | • |     |  | • | • | • • | 281 |

|     | A.4.7 r  | mt_in  |           |     | • • |     | <br> | <br> |       | <br> | • |     |  | • | • |     | 281 |

|     | A.4.8 r  | mt_ou  | ıt        | ••• | ••• | • • | <br> | <br> |       | <br> | • |     |  | • | • |     | 281 |

|     | A.4.9 r  | mt_xc  | hg .      |     | ••• |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 282 |

|     | A.4.10 r | mt_xir | n         |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 282 |

|     | A.4.11 r | mt_xo  | ut.       |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 282 |

|     | A.4.12 r | mt_xx  | chg .     |     |     |     | <br> | <br> |       | <br> | • |     |  |   |   |     | 283 |

|     | A.4.13 c | out .  |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 283 |

|     | A.4.14 c | out32  |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 283 |

|     | A.4.15 c | out8.  |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 284 |

|     | A.4.16 c | outby  | te        |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 284 |

|     | A.4.17 c | outwo  | ord.      |     |     |     | <br> | <br> |       | <br> | • |     |  |   |   |     | 284 |

| A.5 | Alternat | tion . |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 284 |

|     | A.5.1 a  | alt    |           |     |     |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 284 |

|     | A.5.2 a  | altend | 1.        |     |     |     | <br> | <br> |       | <br> | • |     |  |   |   |     | 285 |

|     | A.5.3 t  | talt . |           |     |     |     | <br> | <br> |       | <br> | • |     |  |   |   |     | 285 |

|     | A.5.4 a  | altwt  |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 285 |

|     | A.5.5 t  | taltwt | : <b></b> |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 285 |

|     | A.5.6 c  | disc . |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 286 |

|     | A.5.7 c  | diss . |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 286 |

|     | A.5.8 c  | dist . |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 286 |

|     | A.5.9 e  | enbc   |           |     | ••  |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 287 |

|     | A.5.10 e | enbc2  | •••       |     |     |     | <br> | <br> |       | <br> | • |     |  | • |   |     | 287 |

|     | A.5.11 e | enbc3  |           |     |     |     | <br> | <br> |       | <br> | • |     |  |   |   |     | 287 |

|     | A.5.12 e | enbs   |           |     |     |     | <br> | <br> |       | <br> | • |     |  |   |   |     | 288 |

|     | A.5.13 e | enbs2  |           |     | • • |     | <br> | <br> |       | <br> | • |     |  |   |   |     | 288 |

|     | A.5.14 e | enbs3  |           |     | • • |     | <br> | <br> |       | <br> | • |     |  |   |   |     | 288 |

|     | A.5.15 e | enbt . |           |     |     |     | <br> | <br> |       | <br> |   |     |  |   |   |     | 289 |

|     | A.5.16  | enbt2           | 289 |

|-----|---------|-----------------|-----|

|     | A.5.17  | enbt3           | 289 |

|     | A.5.18  | ndisc           | 290 |

|     | A.5.19  | ndiss           | 290 |

|     | A.5.20  | ndist           | 290 |

| A.6 | Auxilia | ary             | 291 |

|     | A.6.1   | getaff          | 291 |

|     | A.6.2   | getpas          | 291 |

|     | A.6.3   | getpri          | 291 |

|     | A.6.4   | proc_end        | 292 |

|     | A.6.5   | sem_claim       | 292 |

|     | A.6.6   | sem_init        | 292 |

|     | A.6.7   | sem_release     | 292 |

|     | A.6.8   | setaff          | 293 |

|     | A.6.9   | setpri          | 293 |

|     | A.6.10  | wait_int        | 293 |

| A.7 | Other   |                 | 294 |

|     | A.7.1   | BasicRangeError | 294 |

|     | A.7.2   | dtrace          | 294 |

|     | A.7.3   | floaterr        | 294 |

|     | A.7.4   | fmul            | 294 |

|     | A.7.5   | norm            | 295 |

|     | A.7.6   | overflow        | 295 |

|     | A.7.7   | RangeCheckError | 295 |

|     | A.7.8   | rtthreadinit    | 295 |

|     | A.7.9   | BNSeterr        | 296 |

|     | A.7.10  | shutdown        | 296 |

|     | A.7.11  | trap            | 296 |

|     | A.7.12  | unsupported     | 296 |

|    |       | A.7.13   | zero_div                                                                                                         | 297 |

|----|-------|----------|------------------------------------------------------------------------------------------------------------------|-----|

| В  | Mob   | oile Typ | es                                                                                                               | 298 |

|    | B.1   | Descri   | ptors                                                                                                            | 299 |

|    | B.2   | Type N   | Numbers                                                                                                          | 300 |

|    |       | B.2.1    | 0: Numeric Data                                                                                                  | 300 |

|    |       | B.2.2    | 1: Mobile Array                                                                                                  | 301 |

|    |       | B.2.3    | 2: Mobile Channel Bundle                                                                                         | 301 |

|    |       | B.2.4    | 3: Mobile Barrier                                                                                                | 302 |

|    |       | B.2.5    | 4: Mobile Process                                                                                                | 303 |

|    |       | B.2.6    | 5: Mobile Type                                                                                                   | 303 |

|    |       | B.2.7    | 6: Mobile Type Descriptor                                                                                        | 303 |

|    |       | B.2.8    | 7: Mobile Data                                                                                                   | 303 |

|    |       | B.2.9    | 8: Fixed Array                                                                                                   | 303 |

|    |       | B.2.10   | 9: Array Options                                                                                                 | 304 |

|    | B.3   | Opera    | tions                                                                                                            | 304 |

|    |       | B.3.1    | malloc, mrelease                                                                                                 | 304 |

|    |       | B.3.2    | mt_alloc, mt_release                                                                                             | 305 |

|    |       | B.3.3    | mt_clone                                                                                                         | 305 |

|    |       | B.3.4    | mt_in, mt_out                                                                                                    | 305 |

|    |       | B.3.5    | $mt\_lock, mt\_unlock \dots \dots$ | 306 |

|    |       | B.3.6    | mt_sync, mt_enroll, mt_resign                                                                                    | 306 |

|    |       | B.3.7    | mt_bind                                                                                                          | 306 |

|    |       | B.3.8    | mt_resize                                                                                                        | 307 |

| Bi | bligg | raphy    |                                                                                                                  | 308 |

| DI | unog  | ιαμπ     |                                                                                                                  | 300 |

|    |       |          |                                                                                                                  |     |

341

# List of Algorithms

| 1  | Run-queue local enqueue algorithm (wait-free).                 | 153 |

|----|----------------------------------------------------------------|-----|

| 2  | Run-queue local dequeue algorithm (wait-free)                  | 154 |

| 3  | Run queue remote dequeue and batch theft algorithm (wait-free) | 155 |

| 4  | Mailbox enqueue algorithm (wait-free)                          | 160 |

| 5  | Mailbox dequeue algorithm (wait-free)                          | 160 |

| 6  | Channel communication algorithm (wait-free)                    | 162 |

| 7  | Timer expiry algorithm (wait-free)                             | 165 |

| 8  | Channel enabling algorithm (wait-free)                         | 170 |

| 9  | Channel disabling algorithm (wait-free).                       | 171 |

| 10 | Timer disabling algorithm (wait-free)                          | 172 |

| 11 | Alternation finalisation algorithm (wait-free).                | 173 |

| 12 | Event trigger algorithm (wait-free)                            | 174 |

| 13 | Mutual exclusion lock claim algorithm (lock-free)              | 177 |

| 14 | Mutual exclusion lock dequeue algorithm (lock-free)            | 178 |

| 15 | Mutual exclusion lock release algorithm (lock-free)            | 179 |

| 16 | Barrier resignation algorithm (lock-free).                     | 183 |

| 17 | Barrier head access algorithm (wait-free)                      | 185 |

| 18 | Barrier synchronisation count update algorithm (lock-free)     | 185 |

| 19 | Barrier synchronisation algorithm (lock-free).                 | 186 |

| 20 | Barrier completion algorithm (lock-free).                      | 187 |

# **List of Figures**

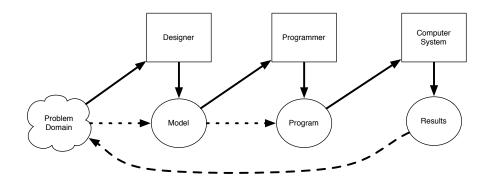

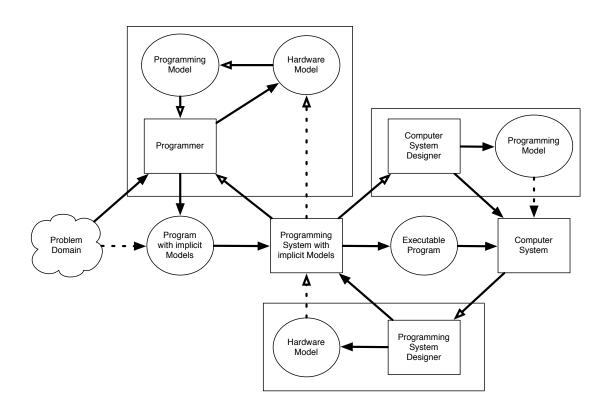

| 1  | Idealised view of abstraction.                                    | 10  |

|----|-------------------------------------------------------------------|-----|

| 2  | View of abstraction reflecting embedded models                    | 10  |

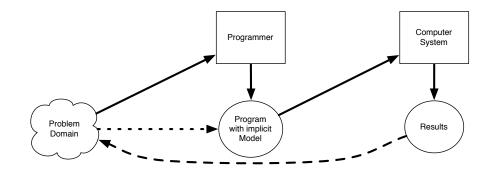

| 3  | Trends in CPU clock speed, transistor count and power consumption | 21  |

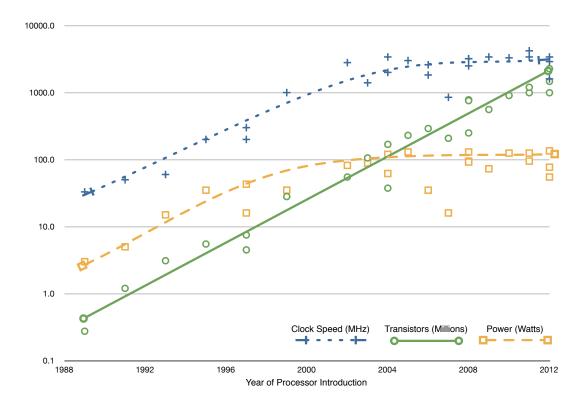

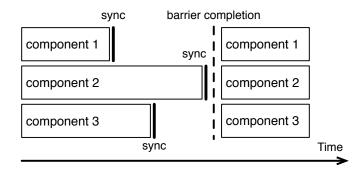

| 4  | Example of barrier synchronisation.                               | 52  |

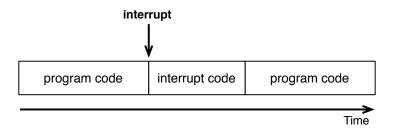

| 5  | Example of interrupt handling                                     | 55  |

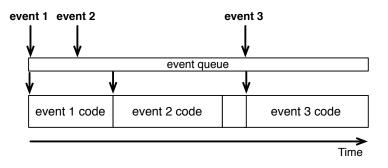

| 6  | Example of event processing                                       | 57  |

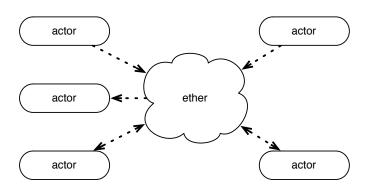

| 7  | Example of messages in Actor model.                               | 59  |

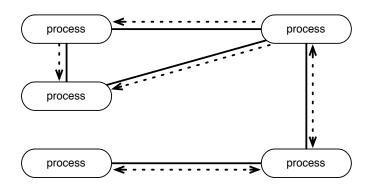

| 8  | Example of messages with channels and processes.                  | 61  |

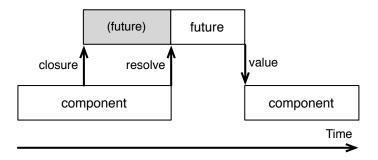

| 9  | Example of futures and resolution.                                | 66  |

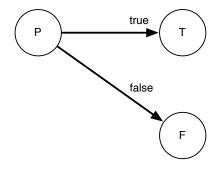

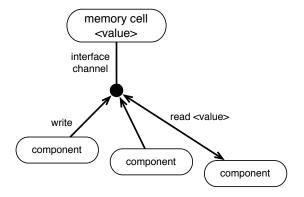

| 10 | Boolean choice                                                    | 67  |

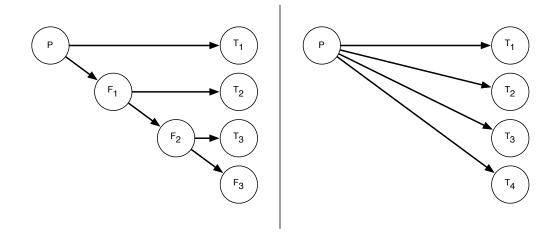

| 11 | Equivalence of boolean and N-way choice.                          | 68  |

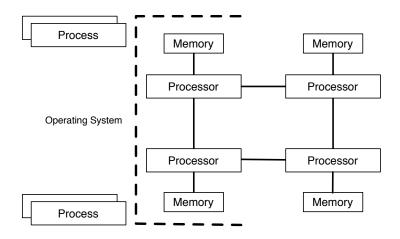

| 12 | Symmetric multiprocessor architecture.                            | 105 |

| 13 | NUMA multiprocessor architecture.                                 | 114 |

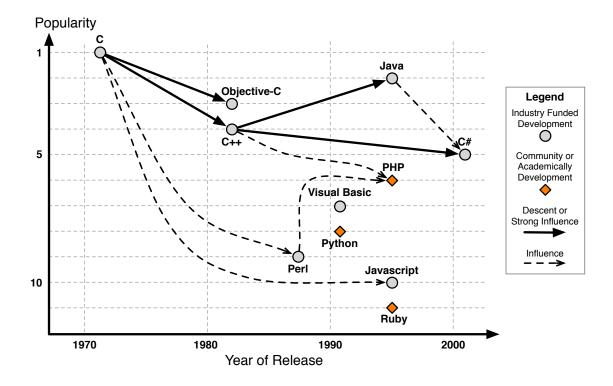

| 14 | Language popularity and heritage                                  | 117 |

| 15 | Abstraction from problem domain to computer system                | 120 |

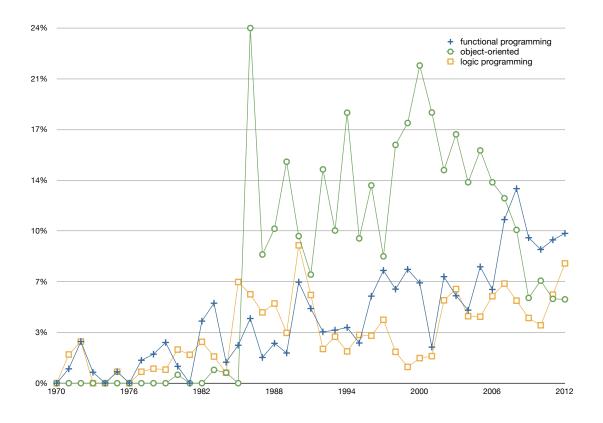

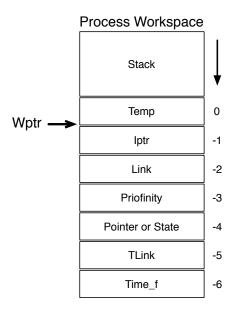

| 16 | ACM SIGPLAN Notice papers relating to programming languages       | 122 |

| 17 | ACM SIGPLAN Notice papers relating to paradigms                   | 123 |

| 18 | ACM SIGPLAN Notice papers relating to concurrency.                | 124 |

| 19 | Statement level concurrency in occam                              | 129 |

| 20 | Channel syntax in occam.                                          | 130 |

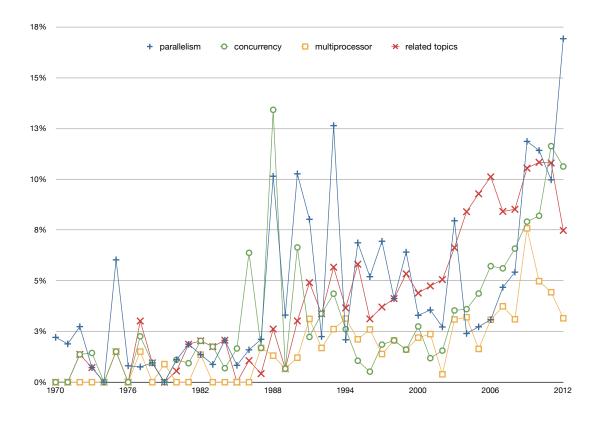

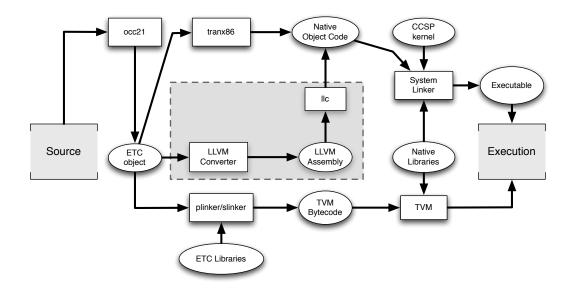

| 21 | KRoC toolchain structure.                                         | 138 |

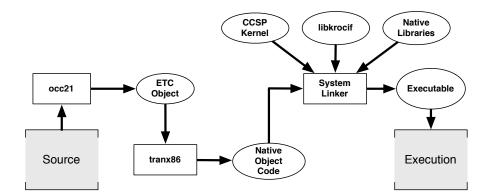

| 22 | Layout of process workspace.                          | 143 |

|----|-------------------------------------------------------|-----|

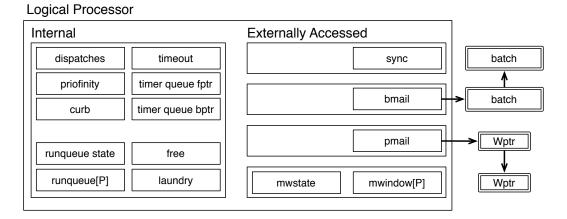

| 23 | Logical processor data structure                      | 147 |

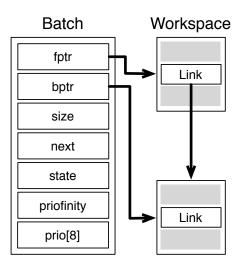

| 24 | Batch data structure layout and fields                | 148 |

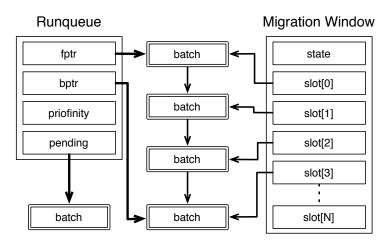

| 25 | Run-queue and migration window structure              | 151 |

| 26 | Timer syntax in occam                                 | 163 |

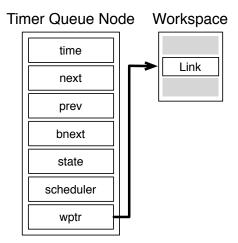

| 27 | Timer queue node structure                            | 163 |

| 28 | Alternation syntax in occam                           | 165 |

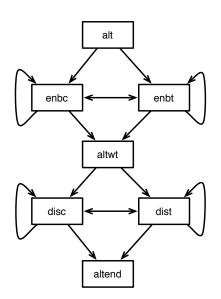

| 29 | Alternation instruction order.                        | 166 |

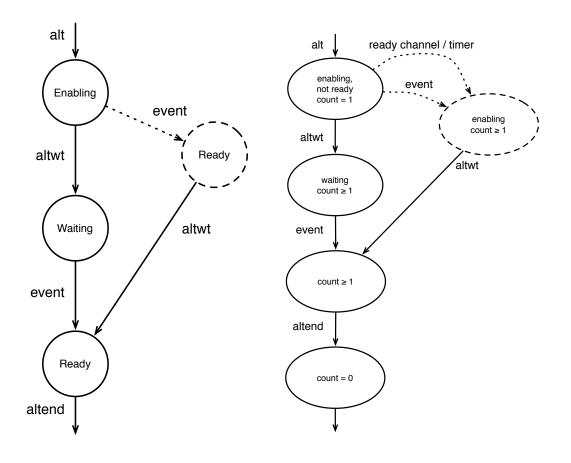

| 30 | Alternation state transitions                         | 167 |

| 31 | Revised alternation state transitions.                | 167 |

| 32 | Extended rendezvous syntax in occam.                  | 174 |

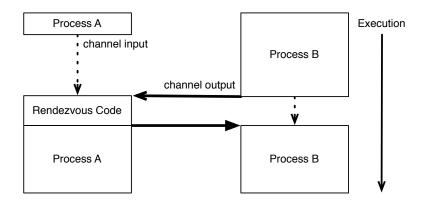

| 33 | Execution of processes performing extended rendezvous | 175 |

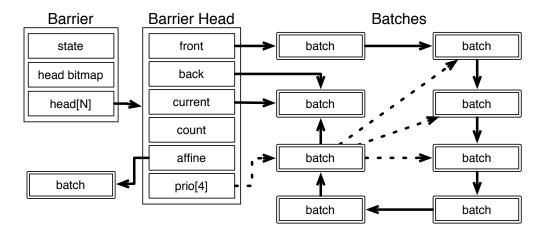

| 34 | Internal structure of barriers.                       | 182 |

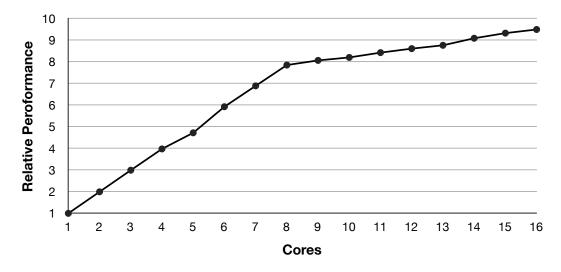

| 35 | Performance of Mandelbrot set benchmark               | 190 |

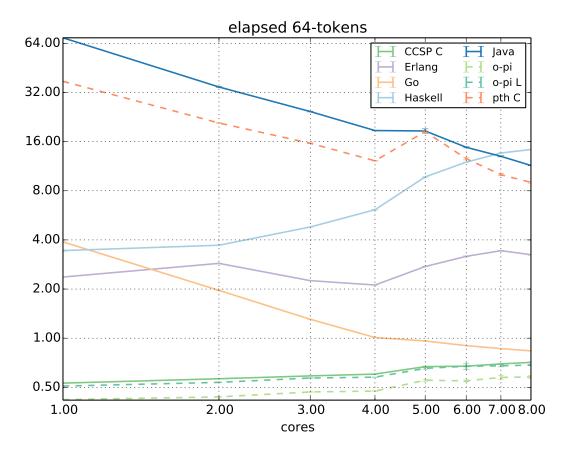

| 36 | Results for process ring with 64 tokens.              | 193 |

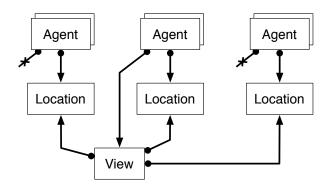

| 37 | Simplified occoids process network.                   | 194 |

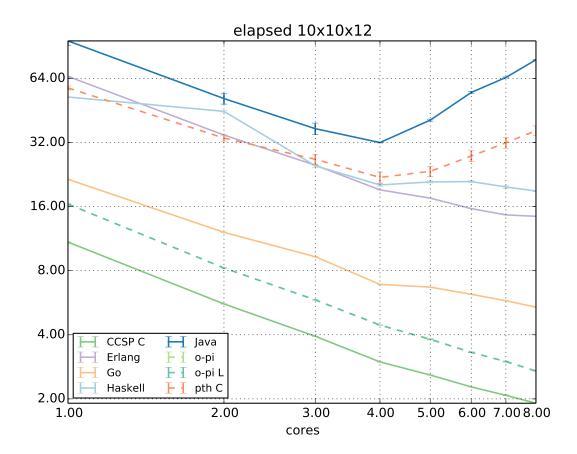

| 38 | Results for agent simulation benchmark (cores).       | 194 |

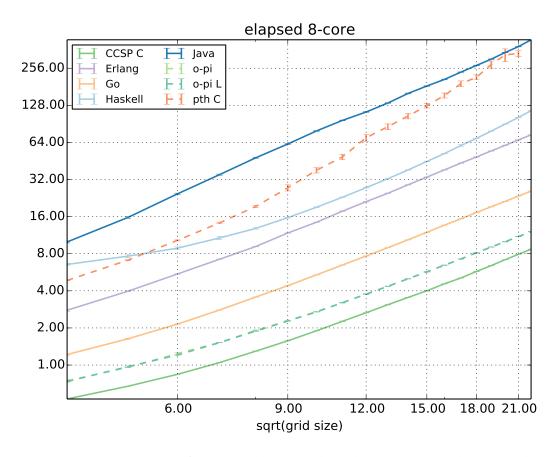

| 39 | Results for agent simulation benchmark (grid size)    | 195 |

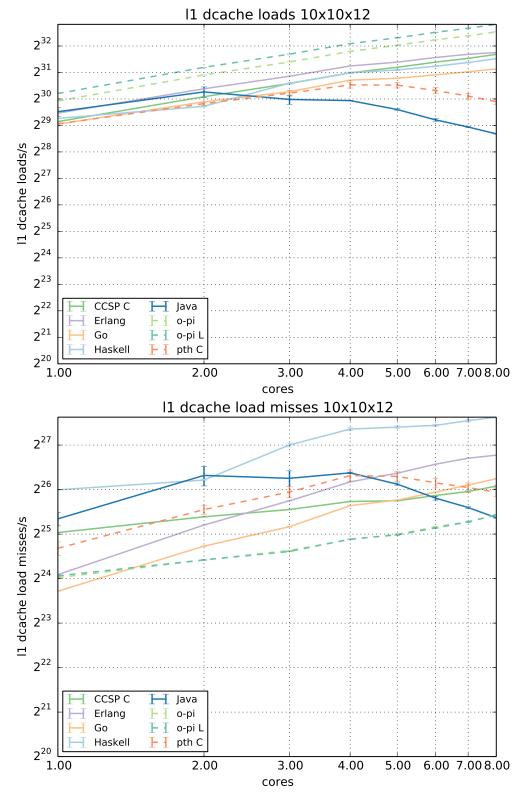

| 40 | Process ring L1 cache loads.                          | 200 |

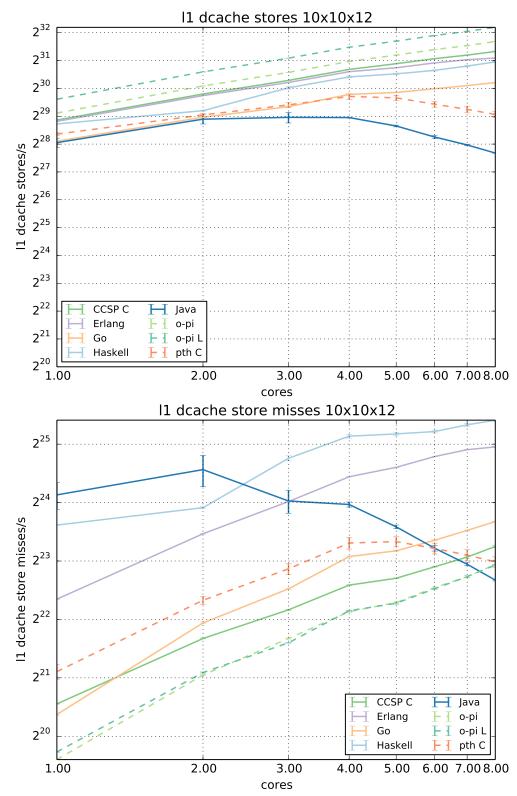

| 41 | Process ring L1 cache stores                          | 201 |

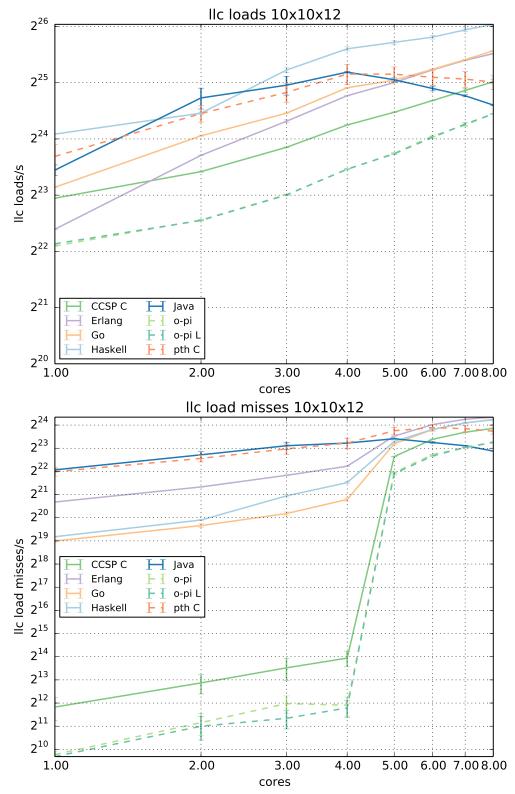

| 42 | Process ring LLC cache loads                          | 202 |

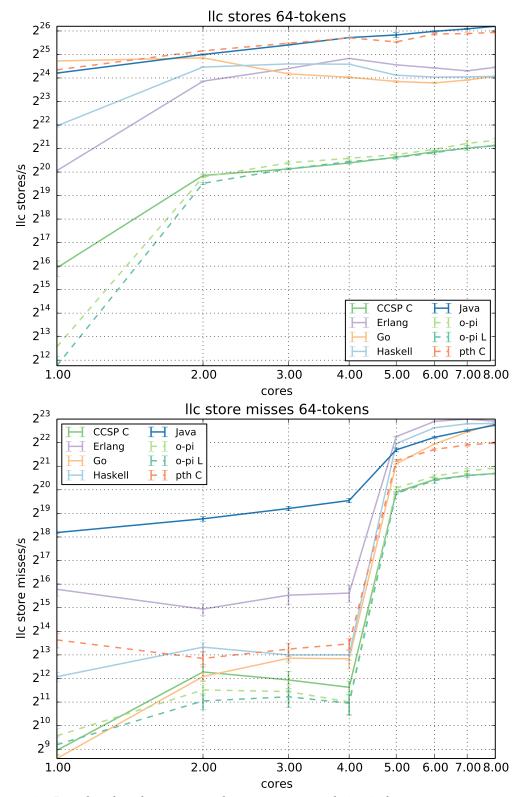

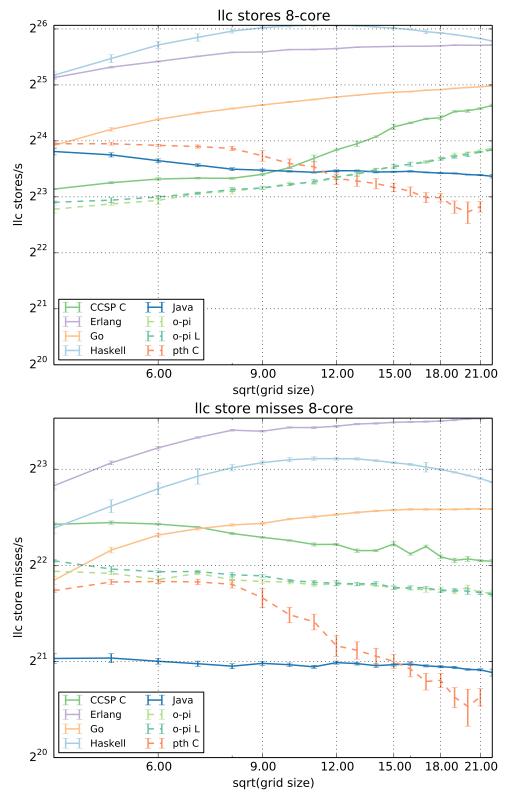

| 43 | Process ring LLC cache stores                         | 203 |

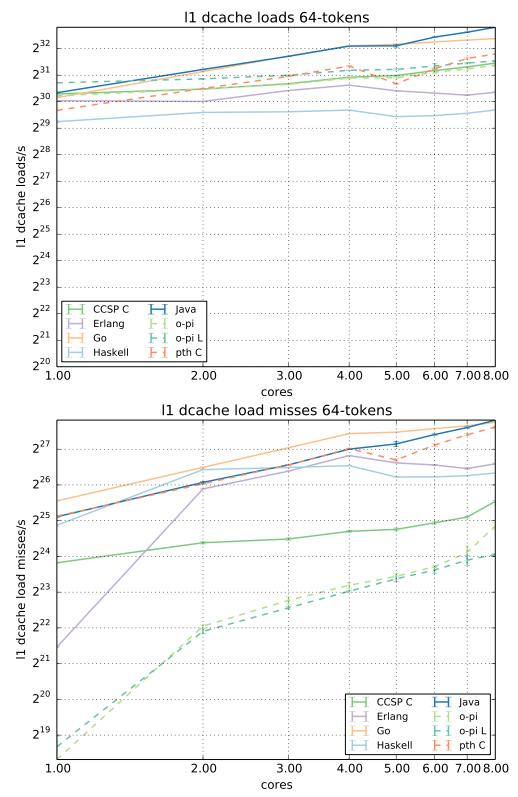

| 44 | Agents (scaling cores) L1 cache loads.                | 204 |

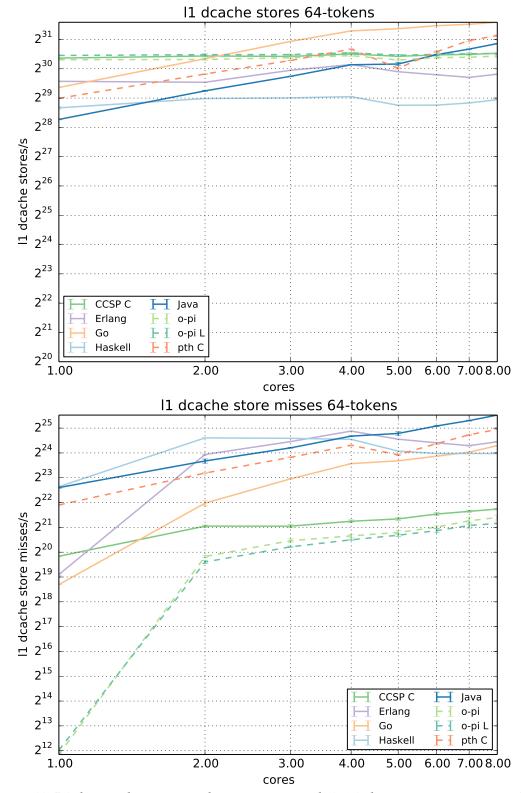

| 45 | Agents (scaling cores) L1 cache stores                | 205 |

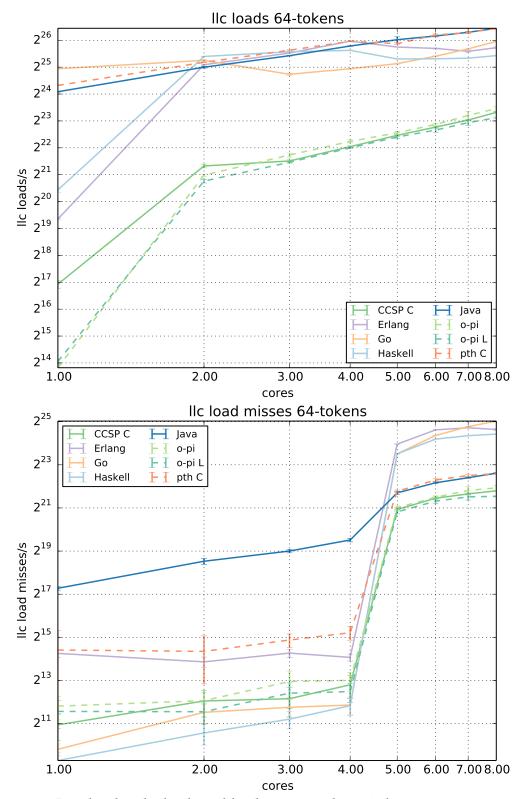

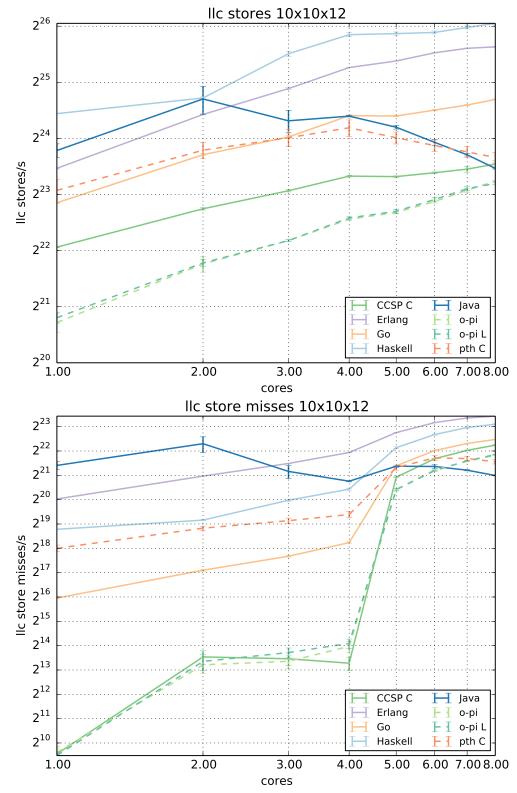

| 46 | Agents (scaling cores) LLC cache loads                | 206 |

| 47 | Agents (scaling cores) LLC cache stores               | 207 |

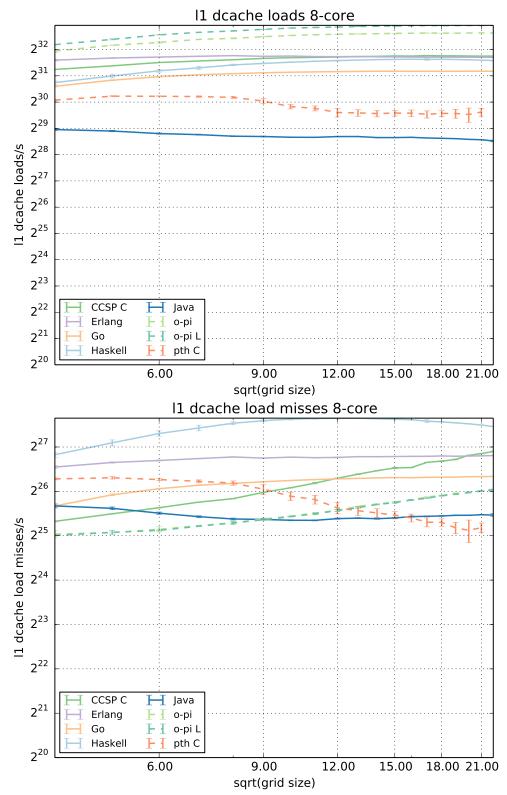

| 48 | Agents (scaling grid size) L1 cache loads.            | 208 |

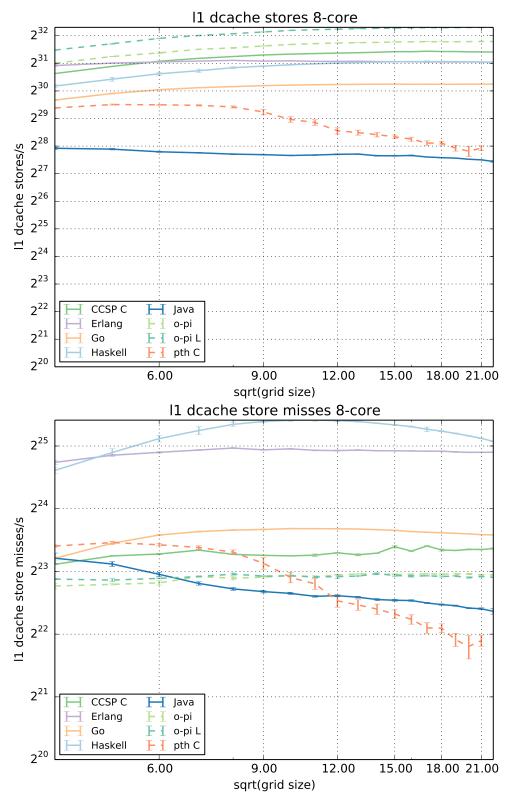

| 49 | Agents (scaling grid size) L1 cache stores            | 209 |

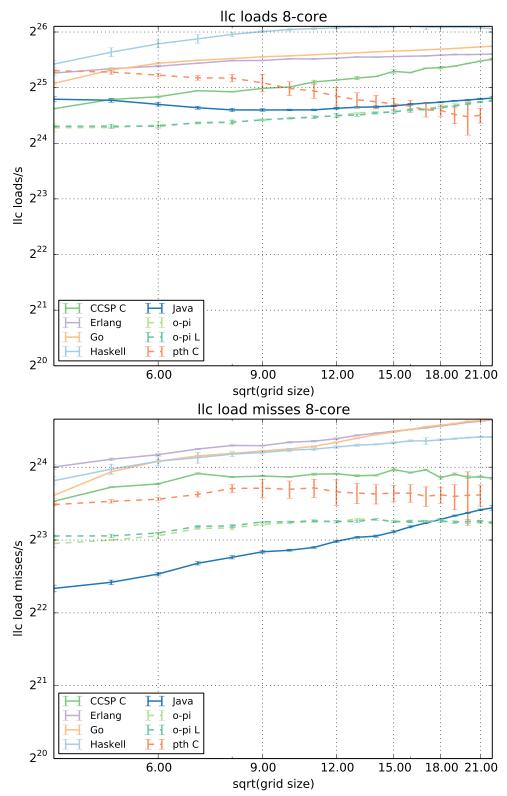

| 50 | Agents (scaling grid size) LLC cache loads.           | 210 |

| 51 | Agents (scaling grid size) LLC cache stores.                               | 211 |

|----|----------------------------------------------------------------------------|-----|

| 52 | Flow through KRoC and Transterpreter toolchains.                           | 215 |

| 53 | Example LLVM function                                                      | 216 |

| 54 | Example Extended Transputer Code                                           | 218 |

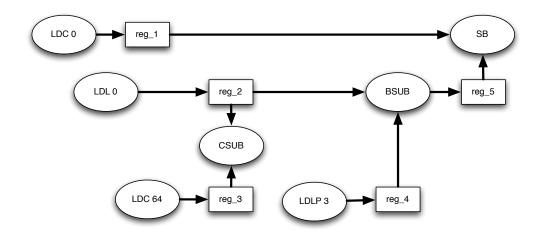

| 55 | Tracing stack utilisation of ETC                                           | 218 |

| 56 | Data flow graph generated from the trace in figure 55                      | 219 |

| 57 | LLVM code illustrating kernel call optimisation issues.                    | 220 |

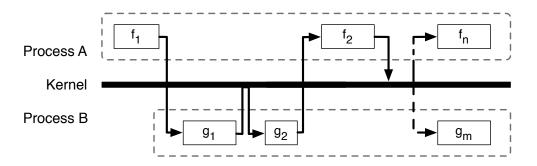

| 58 | Interleaving execution of processes <i>A</i> and <i>B</i>                  | 221 |

| 59 | LLVM code example generated by translation.                                | 222 |

| 60 | LLVM code example showing use of phi node.                                 | 226 |

| 61 | Overview of performance and binary size with LLVM                          | 233 |

| 62 | Virtual machine state data record                                          | 241 |

| 63 | Virtual machine control request protocol.                                  | 242 |

| 64 | Virtual machine control response protocol.                                 | 243 |

| 65 | TEncode identifiers                                                        | 245 |

| 66 | TEncode types.                                                             | 246 |

| 67 | TEncode header fields.                                                     | 247 |

| 68 | TEncode debugging section                                                  | 248 |

| 69 | TEncode in-place decoding structure.                                       | 249 |

| 70 | Bytecode channel bundle protocol definitions.                              | 250 |

| 71 | Decoding bytecode and creating a virtual machine instance for it. $\ldots$ | 254 |

| 72 | Setting up a virtual machine top-level-process                             | 255 |

| 73 | Dispatching instruction on virtual machine                                 | 256 |

| 74 | Implementing tracing of virtual machine instructions                       | 257 |

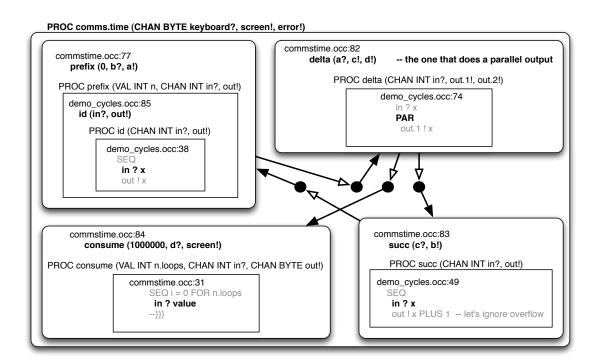

| 75 | Visualisation of commstime.occ.                                            | 258 |

| 76 | Mobile type descriptor layout                                              | 300 |

| 77 | Example mobile array type descriptor                                       | 301 |

|    |                                                                            |     |

## **List of Tables**

| 1 | Cost of memory barrier operations on recent processor architectures | 112 |

|---|---------------------------------------------------------------------|-----|

| 2 | Cost CAS operations on recent processor architectures               | 112 |

| 3 | Languages ranked by popularity                                      | 116 |

| 4 | Communication times for process ring.                               | 191 |

| 5 | Results of execution times benchmark                                | 230 |

| 6 | Binary text section sizes.                                          | 232 |

### Chapter 1

## Introduction

This thesis outlines and demonstrates techniques for the compilation and execution of process-oriented software on multi-core hardware, with an emphasis on efficient use of computer resources (processor time and memory space). This work addresses two connected research questions:

- 1. Can software which uses unbounded concurrency for structure be efficient?

- 2. Can process-oriented programming be used to build scalable software?

The first question applies when software uses a high degree of concurrency without regard for the availability of parallel processing resources. The second question investigates the effect of making more parallel processing resources available to such software.

We use *concurrency* to describe where multiple computations *may* happen at the same time. This is a disambiguation from *parallelism* where multiple computations *do* happen at the same time. Process-oriented programming is a method for applying a high degree of concurrency within software design [228]. It typically produces many more concurrent program elements than there are parallel computing resources to execute simultaneously.

A process-oriented computer program contains multiple isolated software processes which execute concurrently. As processes are isolated from each other all interaction, including information exchange, occurs via explicit communication and synchronisation mechanisms. The explicit nature of interaction in process-oriented programming underpins its ability to manage complexities arising due to concurrency, such as nondeterminism. However these interaction mechanisms represent a potential overhead in the execution of process-oriented software.

Computer hardware is moving from systems with a single programmable computation element or *core*, to multiple programmable parallel computation elements or *multi-core*. A high degree of concurrency is critical to utilising the parallel computing resources made available by multi-core computer processors. If my work consists of many tasks I *can* do at the same time (independent tasks) then given a clone of myself I will be able to *do* all my tasks in half the time.

Commodity computer hardware, programming tools and operating systems do not explicitly support process-oriented programming. This means the basic operations on which process-oriented programs depend have significant overheads. The implication is that process-oriented software is not as efficient as other programming methods and may not be able to achieve equal or superior performance.

In the context of this thesis, *mechanical sympathy* describes the congruence of programming models and computer hardware. A mechanically sympathetic computer program uses computer hardware in efficient manner; progress towards a solution is taken along the path of least resistance. A mechanically sympathetic programming language embeds, or encourages the programmer to use, a programming model which has an efficient mapping to real computer systems.

In this thesis I seek to demonstrate the potential of process-oriented software, by minimizing the amount of processor time, memory space and bandwidth consumed in overheads while achieving the maximum use of available parallel processing facilities. This is important as process-oriented programs have a high degree of mechanical sympathy with present and emerging multi-core computer systems (2.7.5). Additionally these benefits can be exploited by other concurrent programming methods through functional decompositions presented in this thesis (2.4.1) and in related work [228].

#### **1.1 Problem Statement**

In order to fully utilise the parallel processing capabilities of modern computer hardware, computer software must utilise a higher degree of concurrency. *Scalable software* is software which has increased performance, faster execution or more work completed per unit time, when additional parallel computing resources are made available to it. The synchronisation and scheduling overheads of common concurrency mechanisms mean that in order to build scalable software the typical concurrent work unit (grainsize [176, 209]) must be relatively large. For example amortizing the cost of a 10ms synchronisation, reducing it below 5% of execution time, requires a work unit lasting at least 200ms.

By reducing the overheads associated with a class of concurrency mechanisms, programmers will be able to introduce more concurrent elements into software without adversely affecting performance. In turn, such software will make more efficient use of available hardware and have improved performance as a result. Better performance may be reduced execution time, reduced response time or comparable execution time with reduced power consumption as larger numbers of lower powered processing elements are substituted for fewer higher powered ones.

#### 1.2 Limitations

This thesis does not address the issue of designing parallel software or computer algorithms. In this thesis I explain what is meant by process-oriented software and how this work allows process-oriented software designs to make use of multi-core hardware, but do not address the process-oriented design process. I would refer the reader to Adam Sampson's thesis [228] which does much to explain process-oriented software design. Beyond process-oriented design, there is a large body of work on developing parallel algorithms, such as Ian Foster's work [110].

#### **1.3 Contributions**

This thesis makes the contributes the following research contributions:

- D1. Message-passing between concurrent components can be at least one order of magnitude faster than presently implemented in common programming languages or concurrency frameworks. This includes modern multi-processor or multi-core computer hardware.

- D2. The parallel execution potential of software using concurrency for structure can be efficiently extracted. This demonstrates that process-oriented programming can be used to build scalable software.

- D3. Process-oriented programming has a high degree of mechanical sympathy with modern multi-core computer hardware. Mechanical sympathy is a key factor in the applicability, efficiency and adoption of programming languages.

This thesis also makes the following technical contributions:

- T1. Development of a highly efficient scheduler for process-oriented systems on multi-core hardware. The scheduler is designed to support thousands of active processes on commodity hardware using runtime decision making based on heuristics rather than a priori knowledge of the system being scheduled.

- T2. Algorithms for synchronous channel communication with choice on multi-core hardware. These enable communication between pairs of processes using wait-free scheduler interaction and permitting choice in one of the communicating parties.

- T3. Algorithms for choice across channels and timers on multi-core hardware. These allow a process to make a choice over a number of communication channels and a system timer.

- T4. Algorithms for supporting explicit priority groups. These scheduler extensions support priority groups in order to guarantee execution of high priority processes before low priority processes.

- T5. Algorithms for barriers on multi-core hardware with optimisations for cachecoherence and priority. These provide synchronisation between tens of thousands of software processes while reducing the negative cache impact of access to a heavily contended resource.

- T6. Additional performance for the occam-pi programming language through the application of machine independent assembly (LLVM). This provides direction for the compilation of future process-oriented languages.

- T7. Development of virtual machine debugging techniques for process-oriented programming. These provide runtime support for introspective analysis of process-oriented programs.

#### 1.4 Road Map

Chapter 2 examines the motivations for the use of concurrency in software design and support for concurrency in programming languages. This can be seen as a review of related work in concurrent programming techniques and a definition of process-oriented programming. It contains a history and analysis of hardware support for concurrency and the development of programming techniques for managing concurrency. It also establishes tenants of contribution D3 (1.3).

Chapter 3 documents the development of a multi-core scheduler for process-oriented software. It contains algorithms for implementing core elements of process-oriented

software such as communication and synchronisation on multi-core systems. These relate to contributions *D1* through *D3* and *T1* through *T5* (1.3).

Chapter 4 describes methods for compiling and executing process-oriented software on modern computer systems. The focus is on the occam-pi programming language and translating it to machine-independent assembly languages. This relates to contribution T6 (1.3).

Chapter 5 explores potential debugging and tracing techniques for procress-oriented programming. These make use of a virtual machine implementation of occam-pi, such as that provided by the Transterpreter [146]. This relates to contribution *T7* (1.3).

Chapter 6 summarises the conclusions of this thesis and discusses some directions for future research. Attention is given to the direction of current computer software and hardware development.

### Chapter 2

## Concurrency

This chapter is an in-depth survey of concurrency support in programming languages, its origins and trends. The content of this chapter is intended to be accessible to a wide audience, with many sections essentially readable without much, if any, prerequisite knowledge. To support this, programming concepts are, where appropriate, analogised to examples from other domains, for example cookery.

A key purpose of this chapter is to document and analyse a trend towards dataoriented methods in the mechanisms provided for programming concurrency by popular programming languages (see 2.2 and 2.7.2). This trend is rooted in the shared ancestory of popular programming languages, an ancestory which eschews a model for programming concurrency (see 2.7.1). Recent trends in hardware parallelism have motivated the need for mechanisms for programming concurrency (see 2.1.3 and 2.6). This thesis argues that process-oriented programming satisfies the need for a mechanically sympathetic model of programming concurrency on new and emerging computer hardware (see 2.7.5). Furthermore, it argues that process-oriented programming is more appropriate than data-oriented methods while still maintaining support for existing data-oriented programming primitives (see 2.4.1).

This chapter is broad in scope and as such the first-time reader may wish to omit

some sections. For the purpose of understanding other chapters the material on paradigms in section 2.2 and in particular the message-passing paradigm (2.2.2) is essential. From the material in section 2.3, section 2.3.1 on processes, section 2.3.2.4 on messages and section 2.3.3 on choice should be read. The full definition of process-oriented programming in section 2.4 is also essential to this thesis. Finally, the memory synchonisation cost data given in section 2.6.1 may prove useful to understanding the arguments in chapter 3.

#### **Road Map**

Section 2.1 explores two key motivations for the use of concurrency in the design of computer programs: *expression* and *performance*. Expression describes the use of concurrency to address the parallel nature of the world. Performance refers to the use of concurrency to utilise parallel computer hardware. This section also considers recent and on-going trends in computer hardware to increasingly parallel computer systems. These key elements motivate the importance of research on concurrent programming languages and their run-time support.

Section 2.2 describes the main paradigms (styles) of concurrent programming: dataoriented concurrency and message-passing concurrency. Adding to this, section 2.3 details common language operations and primitives for handling concurrency. The intention is to provide a broad overview of distinct methods for introducing and handling concurrency in computer programs. These provide reference for later sections and chapters.

Section 2.4 defines process-oriented programming, a specific form of message-passing concurrency. Critically, the primitives surveyed in section 2.3 are given process-oriented definitions. This section establishes broadly that process-oriented programming is capable of concisely expressing other forms of concurrency. This is necessary to establish the wider applicability of work in this thesis.

Section 2.5 surveys support for concurrent programming in a broad range of popular and general-purpose programming languages. This section provides an integral reference for other sections; however, as a reference, cover to cover reading is not required. The subsequent section, section 2.6, gives an overview of support for concurrent programming in computer hardware. The subsection *Synchronisation* (2.6.1) identifies the costs of using shared memory for inter-processor synchronisation. The subsection *Interconnects* (2.6.2) describes the reasons behind the growth in synchronisation costs in modern computer hardware. These motivate the need to avoid inter-processor communication by using paradigms such as process-oriented programming and appropriate algorithm design as in chapter 3.

Section 2.7 analyses information presented in sections 2.5 and 2.6. The general trend is for minimal support for concurrent programming with a focus on a data-oriented style where support is present. This contrasts with process-oriented programming which uses concurrency as a method for structuring computer software. This trend is analysed with respect to popular programming languages and a critical aspect of programming language design, *mechanical sympathy*, is identified. Finally, key properties of a process-oriented style of programming are highlighted in relation to new and emerging computer architectures. It is postulated that process-oriented software is mechanically sympathetic with trends in hardware development.

#### 2.1 Motivations

The motivations for the use of concurrency in the design and implementation of computer software can be loosely categorised into *expression* and *performance*.

Inherent in the creation of a computer program is the act of modelling a problem domain and mapping between it and a physical computer system. The programmer (or designer) produces a model, an abstraction, of a problem for the computer to solve; this is then expressed such that a computer can produce results or enact a solution. This idealised process can be seen in figure 1. The results produced by the computer are related to the problem domain in a manner determined by the programmer and the quality of the model produced by the designer. In reality the designer and programmer are

Figure 1: Idealised view of abstraction between problem domain and computer system.

Figure 2: Simplified view of abstraction reflecting the reality that programs implicitly derive and embed domain models.

typically the same person, and the modelling step is implicit in the act of programming as in figure 2. That is to say the programmer does not consciously consider the model chosen or its implications. This can be problematic, in particular when the results of the program are to be scientifically rigorous [34].

Very early electronic computers such as ENIAC were programmed by the manipulation of switches and the physical connections between components. This soon gave way to the input of computer programs in the form of instructions typically stored on punched cards. The programmer expressed the problem directly in rudimentary machine operations, *assembly language*, e.g. load *a*, load 4, add, store as *b*. Essentially there was no abstraction between program and computer operations. It takes considerable effort to express complex problems in terms of rudimentary *low-level* computer operations. This lead to the development of *high-level* programming languages. The first of these to see widespread usage was IBM's *FORTRAN* [42]. A key concern in the development of early high-level programming languages was to allow algebraic expressions. A program within the computer translates high-level expressions such as b = a + 4, into low-level assembly code. This program is called a *compiler*.

The introduction of early high-level languages, particularly FORTRAN, sees the introduction of commercial (*industry*) interests into computer programming. High level languages make computer programming more accessible, for example algebraic expression is more widely understood than the decomposition of problems into assembly language. This allows more people to write computer programs and increases the efficiency of existing programmers However, the compiler must be efficient. The assembly produced by the compiler must have similar performance, in terms of memory space and computational time requirements, as that produced by a skilled programmer. High level languages before FORTRAN were not efficient enough to justify their commercial use [43]. Early high-level languages might slow a computer down by a factor of five, an unacceptable slow down when some of the most basic computers cost upward of  $\pounds 200,000$  a year to rent <sup>1</sup>.

High level programming languages allow program text, *source code*, to more closely reflect and express the problem model. A key motivating factor in the development of most programming languages is the ability to clearly express a given problem domain, so that the program can accurately capture the model. This is particularly true of high-level languages developed in the late 1950s and early 1960s. Notable contemporaries to FORTRAN stand out as examples of this:

• *ALGOL* was developed by academia to address what were seen as failings in FORTRAN. Essentially ALGOL focuses on expression of algorithmic computing

<sup>&</sup>lt;sup>1</sup>Based on the rent of a basic IBM 1401 \$30,000 in 1959 and taking into account inflation based on the consumer price index.

for research scientists [41].

- COBOL was developed as a government and industry effort to create a standardised language for business-oriented tasks [208]. It was heavily used in government and commercial projects, to such an extent that more than 40 years after its inception it is still the 24th most popular programming language by usage [246].

- *Lisp* was developed by academia to express computation in a manner consistent with the *lambda-calculus*, which permits reasoning about the computability of mathematical functions [177]. The *Church-Turing thesis* relates the lambda-calculus to *Universal Turing Machines* showing that both express the same functions, and that functions can express all arithmetically computable operations. This theory underpins the discipline of *functional programming* which Lisp embodies.

Assembly languages are generally described as second generation languages, with first generation referring to machine operations represented directly by signals within the computer, so called *machine code*. Languages such as FORTRAN and ALGOL are third generation languages. Much research in the 1960s focused on structuring programs in third generation languages. One of the most well-known and widely used developments of this era is a programming paradigm called *object-oriented programming* [66]. Starting with SIMULA in 1968 [86] and exemplified by Smalltalk in 1973 2.5.27, object-orientation structures a program as a set of interacting objects. Loosely, each object represents a concrete or abstract concept and has a defined interface of operations it can perform on the behalf of other objects. For example, a toaster object might provide an interface with *set temperature* and *toast* operations. The inner workings of the toaster are hidden from other objects in the system. This is known as *encapsulation*. In principle this allows objects to be built and tested in isolation before being put together to produce larger programs.

High-level languages provide functionality not directly available in machine hardware. These functions may be provided by a *runtime system* (*RTS*), a library of prepared code which integrates with a program as it executes, at *runtime*. The invocation of the runtime system is (at least in part) embedded as part of the translation from high-level syntax to machine instructions. This occurs without the programmer needing to be aware of it taking place. For example if a given computer processor does not support integer division the programming environment may embed a call to a library function whenever the programmer divides two integers. Whether the hardware supports the operation or not, the result of the higher-level programming statement is always the same (albeit the library function may take longer to execute).

The runtime system may provide a *virtual machine* which simulates an idealised computer and hides the details of any particular computer hardware. This simplifies the task of converting a programming language into machine instructions as it need only be converted to one type of machine, the virtual one. However making the virtual machine representation of the program execute with the same performance as a direct conversion from language to machine instructions is non-trivial [115, 61, 39].

From the 1970s through to the early 1980s research and development focused heavily on third generation languages. The C programming language was released in 1973 (2.5.4) and gains popularity for *systems programming*, the development of software which controls a computer's hardware and provides functionality to other programs. By the early 1980s C has two major descendents, C++ (2.5.6) and Objective-C (2.5.20) both of which add object-oriented extensions to the language. The 1970s also sees the development of fourth and fifth generation languages; both of these aim to further remove the programmer from the low-level detail of the computer. Fourth generation languages are predominantly data processing languages focused on business needs; a third generation language is used in a defined architecture such that programs can be combined and reused and support tools exists to manage data and programs together [171]. Fifth generation languages and logic programming languages, such as Prolog, remove the programmer from specifying a solution to a problem, instead the properties of a valid solution are specified and the computer provides valid solutions within these *constraints* [75]. Despite the significant effort invested in fourth and fifth generation programming language research and development they have gained very limited popularity [246]. This is an important observation that is addressed in the analysis presented in section 2.7.

The need to handle and exploit concurrency emerges almost as soon as the first electronic computers are put in to use and gains weight as a research topic as computers grow in scale and speed [83, 90, 109, 119, 106]. Computers are constructed from multiple concurrent components which do not all work at the same speed. Rapid advances in early electronic computers quickly exposed these operational asymmetries. This creates a need to *express* the concurrency present in the computer so that it can be managed. Further to this, with the relatively high cost of computers and associated overheads<sup>2</sup> prior to the introduction of microcomputers in the 1980s, it was desirable that all aspects of the computer be utilised as fully as possible. This requires that multiple concurrent activities take places to maximise *performance*.

#### 2.1.1 Expression

Expressive power in programming languages is conceptually the same as in natural language. For example, consider the instruction "bake a sponge cake", this is a high-level statement than relies on the knowledge of what it is to bake and what a sponge cake is and how the two can be related. This instruction can be decomposed into simpler components, e.g. cream together 100 grams of sugar and butter, beat in an egg, combine 100 grams of flour, place in a baking tin, place the tin in an oven at 180 degrees celsius for 25 minutes. Each of these simpler instructions relies on further conceptual and specialised knowledge. Decomposition of these instructions can be continued until a base level is reached, e.g. turn 90 degrees right, lift right arm 50cm, move right arm 30cm forward, grasp cupboard handle in right hand, move right arm backward 30cm, and so on. This is essentially *assembly language*. Each level of decomposition moves

<sup>&</sup>lt;sup>2</sup>Wages for the team of programmers and administrators along with the cost of electricity.

from an abstract generalised solution to a concrete implemented solution. However successive levels of decomposition obscure the high-level intent; the entire sequence of operations must be read and considered in order to realise that the intent.

With respect to figure 1, if the problem domain contains concurrency then the designer can either include this in the model, or abstract it away. Support for expressing concurrency in the programming language, programming paradigm and its support tools, broadly the *programming system*, will affect the designer's decision in this respect. This is particularly true for implicit models as per figure 2.

Concurrency is generally present in any model which interacts with external entities. An external entity is anything outside the control of the computer. Critically this is a concern for any computer program that interacts with a user, as the user can potentially produce new input or behaviour at any point. This concern is often mitigated by only allowing user interaction at defined points, but this abstraction can reduce the quality of the interaction experienced by the user. In many cases this abstraction is not acceptable, computer games being one prime example. While playing a computer game, the player expects it to respond immediately to their input.